はじめに

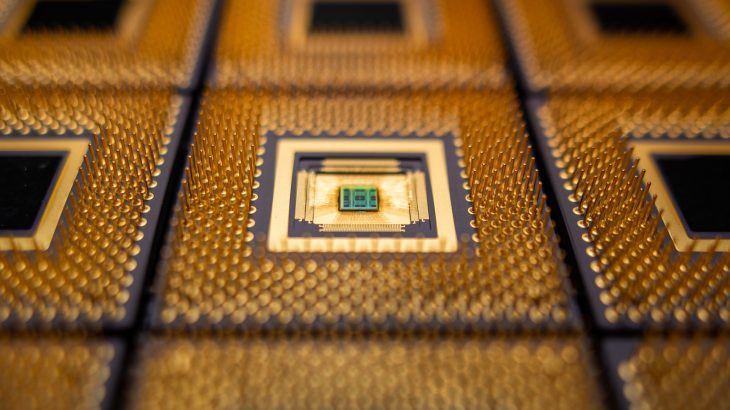

プリンストン大学の研究チームが、計算速度を向上させながら、電力使用量を削減したニューラルネットワーク専用の新しいチップを作成しました。今後、自動車やスマートフォンなどのリモートデバイスに高度なアプリケーションを搭載することに役立つことが期待されています。

Rethinking microchips’ design pushes computing to the edge

https://engineering.princeton.edu/news/2021/02/24/rethinking-microchips-design-pushes-computing-edge

概要

プリンストン大学の研究チームが、ニューラルネットワーク型のAIシステムの普及に合わせて、速度を大幅に向上させながら、電力使用量を削減できるチップを作成しました。今後、有効に活用できるソフトウェアを開発していくととで、より広範に使用できるようにしていきます。

チップの特性

AIをリアルタイムで日常的に利用するためには、プライバシー保護と遅延を避けるために、計算自体をエッジに移動することが必要です。そのためにはチップそのもののエネルギー効率の向上とパオフォーマンスの向上が求められます。

電力需要とリモートサーバーからのデータ交換の必要性の両方を削減することに成功しました。新たに作られたチップは、ドローンや高度な言語翻訳者向けのパイロットソフトウェアなどの人工知能アプリケーションをコンピューティングインフラストラクチャの最先端に持ち込むことができます。

チップの改良点

電力消費量をさげ、メモリストレージの必要性を削減するために、研究チームは計算を行い、同じ場所にデータを保存するチップを新たに設計しました。この手法は一般的にインメモリコンピューティングと呼ばれ、専用メモリと情報を交換するために使用されるエネルギーと時間を削減します。

ただし、この手法は効率を高めますが、小さな領域に2つの機能を詰め込むため、電圧変動や温度スパイクなどの原因による破損に敏感なアナログ操作に依存することになります。そのため、研究チームは、トランジスタではなくコンデンサを使用してチップを設計しました。電荷を蓄えるコンデンサであれば、より高精度に製造でき、電圧の変化による影響をあまり受けないためです。

また、アナログコアを実際の利用にあわせて、0と1で表されるデジタルアーキテクチャに効率的に統合する必要があります。デジタルアーキテクチャは問題に応じて方程式を組みなおすことができますが、それに対して、アナログアーキテクチャは方程式をはじめらから構築しているようなものです。そのため、デジタルアーキテクチャとアナログアーキテクチャとを組み合わせることには、困難が生じます。研究チームはデジタルシステムを中心にすえ、ニューラルネットワークをアナログチップで動作させることで解決しました。

今後の展望

両者を組み合わせることで、よい結果を得ることができることは明らかになりました。今後、アナログとデジタルの二つをシームレスかつ効率的に統合できるソフトウェアシステムを開発することが求められています。

まとめ

今後、ニューラルネットワークモデルのAIは日常的に利用されることが期待されています。より効率的なAIチップの開発が勢力図を決めるとも考えられており、日本で最も有力ともいわれるプリファードネットワークでは専用のAIチップの開発が現在の主力事業にもなっています。効率的なAIチップの開発は注視すべき分野といえます。